Dlaczego pamięć stała się głównym wąskim gardłem w serwerach

Jak ewoluowało wąskie gardło – od CPU do pamięci

Przez wiele lat podstawowym ograniczeniem wydajności serwerów była moc obliczeniowa procesora. Wraz z upowszechnieniem wielordzeniowych CPU, akceleratorów GPU oraz specjalizowanych układów (np. TPU, NPU) sytuacja zaczęła się stopniowo odwracać. Nowoczesne procesory z dużą liczbą rdzeni często nie są już w pełni wykorzystywane, bo czekają na dane z pamięci.

Tempo wzrostu liczby rdzeni i przepustowości wewnętrznych cache L1/L2/L3 jest wyraźnie wyższe niż wzrost przepustowości klasycznych kanałów pamięci DRAM. W praktyce oznacza to, że różnica pomiędzy czasem dostępu do danych w cache a czasem dostępu do RAM rośnie. Jeszcze większa przepaść dzieli RAM i pamięci masowe typu SSD lub HDD.

Powstaje klasyczny „mur pamięci” – CPU jest szybki, ale przez większość czasu czeka na dane. W zastosowaniach intensywnie wykorzystujących pamięć, takich jak analityka in-memory, systemy rekomendacyjne czy trenowanie modeli AI, to właśnie opóźnienia i przepustowość pamięci głównej stają się dominującym ograniczeniem skalowania.

Dobrym przykładem jest hurtownia danych trzymana w całości w pamięci (in-memory). Na papierze serwer z 64 rdzeniami powinien z łatwością obsłużyć wiele zapytań analitycznych jednocześnie. W praktyce zapytania „duszą się” na dostępie do RAM – rośnie liczba przerwań cache miss, rośnie średnie opóźnienie na operację, a rdzenie czekają. Rozbudowa CPU niewiele tu pomaga, bo problemem jest dostęp do danych, a nie liczba jednostek wykonawczych.

Granice współczesnego DRAM i tradycyjnej szyny pamięci

Klasyczna architektura serwera x86 lub ARM opiera się na kilku kontrolerach pamięci wbudowanych w CPU. Każdy kontroler obsługuje ograniczoną liczbę kanałów, a każdy kanał – ograniczoną liczbę slotów DIMM. To fizyczna bariera, której nie da się przekroczyć bez zmiany architektury magistral.

Gdy rośnie pojemność potrzebnej pamięci, producent serwera ma ograniczone możliwości: może dodać więcej modułów o większej gęstości (droższe, bardziej prądożerne, trudniejsze do chłodzenia) albo wprowadzić konstrukcje wielogniazdowe (więcej CPU, więcej kontrolerów, wyższy koszt i złożoność). Dodatkowo przy bardzo dużej liczbie modułów DRAM pojawia się problem stabilności sygnału, długości ścieżek i opóźnień – nie wszystko da się „podkręcić” bez konsekwencji.

Do tego dochodzi aspekt energetyczny. Gęste konfiguracje DRAM przy dużych taktowaniach generują znaczące ilości ciepła i wymagają stale zasilania oraz odświeżania komórek. W centrach danych, gdzie liczy się każdy wat, duże banki DRAM stają się istotnym składnikiem TCO – zarówno po stronie energii, jak i chłodzenia.

Kolejnym ograniczeniem są złożone topologie pamięci, takie jak NUMA (Non-Uniform Memory Access). Dostęp do „lokalnej” pamięci przypisanej do danego gniazda CPU jest szybki, ale dostęp do pamięci znajdującej się przy innym gnieździe ma większe opóźnienia i niższą przepustowość. Uzyskanie stabilnej wydajności wymaga precyzyjnego przypisywania procesów i ich pamięci do konkretnych węzłów NUMA, co komplikuje konfigurację systemu i oprogramowania.

Skutki wąskich gardeł dla firm i zespołów IT

Gdy barierą staje się pamięć, typowy odruch to dokładanie kolejnych serwerów zamiast rozszerzania pamięci w istniejących. Zamiast jednego dobrze „dopchniętego” pamięcią serwera, organizacja kupuje trzy mniejsze. Powoduje to zwiększenie liczby licencji, urządzeń sieciowych, portów, obudów, a także kosztów utrzymania i monitoringu.

W środowiskach, gdzie licencje oprogramowania są powiązane z liczbą rdzeni CPU (np. klasyczne bazy danych komercyjnych), pojawia się dodatkowy problem. CPU są niedociążone, bo serwer czeka na pamięć, ale licencja jest naliczana per rdzeń, nie per wykorzystany cykl. Organizacja płaci za moc obliczeniową, której w praktyce nie jest w stanie efektywnie zużyć.

Dla usług czasu rzeczywistego, systemów AI czy analityki strumieniowej, gdzie liczy się niskie opóźnienie i przewidywalność, wąskie gardła pamięci stają się szczególnie bolesne. Każda nieprzewidziana kolejka przy dostępie do RAM czy storage przekłada się na wyższy time-to-response i konieczność nadbudowy złożonych mechanizmów cache’owania w aplikacji. Pojawia się presja na zmiany architektury systemów, a nie tylko sprzętu.

Podstawy technologii pamięci: DRAM, NAND, MRAM i ich miejsce w hierarchii

Hierarchia pamięci w skrócie

Nowoczesny serwer funkcjonuje na bazie hierarchii pamięci, w której różne warstwy równoważą szybkość, pojemność, koszt i trwałość. Zwykle wygląda to następująco:

- rejestry CPU – najszybsze, najmniejsza pojemność, najsilniej powiązane z logiką wykonawczą,

- cache L1/L2/L3 – bardzo szybkie, ale ograniczone pojemnościowo, zbudowane z SRAM,

- pamięć główna DRAM – główny obszar pracy systemu, ulotny, relatywnie szybki,

- pamięć masowa SSD/HDD – duża pojemność, wyższe opóźnienia, nieulotność,

- pamięci zewnętrzne / chmura storage – jeszcze większa pojemność, najwyższe opóźnienia.

Cała sztuka projektowania architektury serwera polega na takim zestawieniu tych warstw, aby gorące dane możliwie jak najczęściej znajdowały się blisko CPU (w cache / DRAM), a rzadko używane – w tańszych, wolniejszych warstwach. Każda nowa technologia pamięci próbuje „wskoczyć” w tę hierarchię i przesunąć granicę kompromisu pomiędzy szybkością, pojemnością, kosztem i trwałością.

MRAM i interfejs CXL dokładnie w tym miejscu wprowadzają jakościową zmianę: pozwalają zdefiniować nowe poziomy pamięci – nieulotnej, ale niemal tak szybkiej jak DRAM – i podłączyć je do CPU w elastyczniejszy sposób niż dotychczas.

DRAM – zalety i ograniczenia

DRAM pozostaje podstawową technologią pamięci głównej ze względu na korzystny kompromis pomiędzy szybkością a kosztem. Charakteryzuje się niskimi opóźnieniami rzędu dziesiątek nanosekund i wysoką przepustowością, co czyni ją odpowiednią dla pracy systemu operacyjnego, baz danych i aplikacji.

Jednocześnie DRAM jest pamięcią ulotną. Komórki oparte na kondensatorach wymagają ciągłego odświeżania, aby utrzymać zapisane bity. W przypadku zaniku zasilania zawartość pamięci DRAM znika. To ogranicza możliwości stosowania DRAM jako trwałego repozytorium danych, szczególnie w aplikacjach wymagających wysokiej spójności.

Ograniczeniem DRAM jest również skalowalność pojemności. Każdy kanał pamięci ma limit liczby obsługiwanych modułów, a rosnąca gęstość chipów wiąże się z większym zużyciem energii i wyzwaniami produkcyjnymi. Przy rosnącej liczbie rdzeni CPU utrzymanie proporcjonalnej ilości pamięci na rdzeń staje się coraz trudniejsze i droższe.

NAND (SSD) – kiedy staje się wąskim gardłem

Pamięci NAND, stosowane w SSD, zapewniły znaczący skok w stosunku do klasycznych dysków HDD, ale wciąż są rzędy wielkości wolniejsze od DRAM, jeśli chodzi o opóźnienia. Zapis i odczyt wymaga operacji na całych blokach, a liczba cykli programowania/kasowania jest ograniczona. Dlatego kontrolery SSD stosują złożone mechanizmy wyrównywania zużycia (wear leveling) oraz buforowania.

Przy intensywnym zapisie NAND staje się krytycznym punktem architektury. I/O jest kolejkowane, a różnica pomiędzy dostępem sekwencyjnym a losowym może być bardzo duża. W systemach bazodanowych czy logujących dane w sposób losowy, SSD oparte na NAND mogą być mocno obciążone i powodować skoki opóźnień.

Nowoczesne SSD NVMe korzystające z PCIe znacząco poprawiają przepustowość w porównaniu z klasycznymi dyskami SATA lub storage sieciowym, ale nie rozwiązują problemu fundamentalnych opóźnień pamięci NAND. W dodatku SSD pozostają urządzeniami blokowymi, postrzeganymi przez system jako storage, a nie rozszerzenie pamięci głównej.

Gdzie potencjalnie „wskakuje” MRAM w tej układance

MRAM (Magnetoresistive RAM) to pamięć nieulotna, która pod względem parametrów ma szansę zbliżyć się do DRAM bardziej niż NAND. W założeniu MRAM może oferować:

- opóźnienia znacznie niższe niż SSD i bliższe DRAM,

- nieulotność – dane pozostają po zaniku zasilania,

- wysoką wytrzymałość na cykle zapisu, wyższą niż NAND,

- niższe zużycie energii statycznej, bo nie wymaga odświeżania jak DRAM.

To otwiera kilka możliwych ról MRAM w serwerach:

- rozszerzenie pamięci głównej – jako „wolniejsza”, ale nieulotna warstwa obok DRAM,

- nieulotny cache – bufor między RAM a storage, który przetrwa restart czy awarię,

- warstwa pośrednia w hierarchii – coś pomiędzy klasycznym RAM a SSD/NVMe.

Dla baz danych, systemów transakcyjnych i aplikacji wymagających persystencji danych w czasie rzeczywistym, MRAM może mieć szczególne znaczenie. Możliwość zapisu trwałego danych z opóźnieniami zbliżonymi do RAM zmienia sposób projektowania logów transakcyjnych, checkpointów czy mechanizmów odzyskiwania po awarii.

Czym jest MRAM: zasada działania, odmiany, mocne i słabe strony

Podstawy działania MRAM (magnetoresistive RAM)

MRAM przechowuje bity nie w kondensatorach, lecz w strukturach magnetycznych. Podstawowym elementem jest komórka zwana MTJ (Magnetic Tunnel Junction), składająca się z dwóch warstw ferromagnetycznych oddzielonych cienką barierą izolującą. Jedna warstwa ma stały kierunek namagnesowania, druga może zmieniać ten kierunek.

Stan logiczny (0 lub 1) odpowiada relatywnemu ustawieniu wektorów magnetyzacji tych dwóch warstw. Gdy są równoległe, opór elektryczny jest inny niż wtedy, gdy są antyrównoległe. Odczyt polega na pomiarze oporu, zapis – na zmianie stanu magnetyzacji warstwy „swobodnej”. Dzięki temu MRAM jest pamięcią nieulotną: brak zasilania nie zmienia stanu magnetycznego komórek.

W przeciwieństwie do DRAM, MRAM nie wymaga ciągłego odświeżania zawartości, co redukuje zużycie energii w stanie spoczynku. W porównaniu z NAND, zapis jest mniej destrukcyjny dla struktury nośnika, co przekłada się na większą wytrzymałość na cykle zapisu.

Na rynku istnieje kilka klas pamięci nieulotnych (NVM), m.in. ReRAM (oparta na zmianie oporu), PCM (Phase-Change Memory), 3D XPoint (wykorzystywana w niektórych produktach jako pamięć persystentna). MRAM wyróżnia się właśnie magnetycznym mechanizmem przechowywania danych, co ma konsekwencje dla prędkości, trwałości i sposobu integracji z procesami technologicznymi półprzewodników.

Odmiany MRAM (STT‑MRAM, SOT‑MRAM i inne)

Najpopularniejszym obecnie podejściem do MRAM jest STT-MRAM (Spin-Transfer Torque MRAM). W tej technologii zapis bitu odbywa się przez przepływ prądu o odpowiedniej polaryzacji przez komórkę MTJ. Spin elektronów przenosi moment magnetyczny, który „przełącza” orientację magnetyzacji warstwy swobodnej.

STT-MRAM jest relatywnie dobrze opanowana produkcyjnie i pojawia się w układach embedded, mikrokontrolerach czy specyficznych zastosowaniach serwerowych (np. nieulotne bufory). Jej zaletą jest stosunkowo prosty model integracji z istniejącymi procesami CMOS i możliwość uzyskania czasów odczytu i zapisu bliższych DRAM niż w przypadku NAND.

SOT-MRAM (Spin-Orbit Torque MRAM) wykorzystuje inny mechanizm – moment spinowo-orbitowy – który pozwala potencjalnie na jeszcze szybsze przełączanie i mniejsze zużycie energii. Zapis odbywa się poprzez prąd przepływający w warstwie ciężkiego metalu, co generuje efekt spinowy wpływający na warstwę magnetyczną.

SOT-MRAM zapowiada się obiecująco w kontekście wysokich częstotliwości i bardzo szybkich zapisów, ale jest trudniejsza w produkcji i wciąż w fazie intensywnego rozwoju. Różne odmiany MRAM różnią się kompromisem między gęstością zapisu, prędkością, zużyciem energii i złożonością procesu technologicznego.

Kluczowe parametry MRAM w zastosowaniach serwerowych

Przy ocenie przydatności MRAM w serwerach kluczowe są trzy grupy parametrów: czas dostępu i przepustowość, wytrzymałość na zapis oraz zużycie energii.

Opóźnienie dostępu w MRAM zwykle mieści się pomiędzy DRAM a NAND, choć konkretny poziom zależy od implementacji. W zastosowaniach serwerowych liczy się nie tylko średnie opóźnienie, ale też jego stabilność. MRAM ma potencjał zapewnić znacznie mniejszą zmienność opóźnień (latency tail) niż SSD NAND, co przekłada się na przewidywalność zachowania systemu.

Wytrzymałość na cykle zapisu w MRAM jest zwykle dużo wyższa niż w NAND. Dla obciążeń intensywnie zapisujących (logi, bazy danych, systemy kolejkowe) oznacza to mniejsze ryzyko przedwczesnego zużycia nośnika i prostsze modele zarządzania żywotnością. Może to zmienić sposób projektowania warstw zapisu i buforowania.

Ograniczenia i wyzwania MRAM

Choć MRAM wygląda atrakcyjnie jako „złoty środek” pomiędzy DRAM a NAND, obecny stan technologii niesie ze sobą istotne ograniczenia, które spowalniają jej szerokie wejście do serwerów.

Po pierwsze, gęstość upakowania komórek MRAM jest nadal niższa niż w przypadku NAND, a często także niższa niż w nowoczesnych układach DRAM. Przekłada się to na wyższy koszt jednostki pojemności. Producenci stopniowo poprawiają ten parametr, przechodząc na mniejsze procesy litograficzne i bardziej zaawansowane struktury warstw magnetycznych, ale dystans w stosunku do NAND pozostanie znaczący.

Po drugie, zapisy w MRAM, choć wytrzymalsze niż w NAND, nadal wymagają stosunkowo wysokich prądów przełączających. Szczególnie w STT-MRAM, przy dużych macierzach i intensywnym zapisie, pojawiają się wyzwania cieplne i energetyczne. SOT-MRAM ma tu przewagę, ale jej proces produkcyjny nie jest jeszcze tak dojrzały.

Po trzecie, integracja MRAM jako pamięci masowej lub rozszerzenia pamięci głównej wymaga dopracowanego ekosystemu: kontrolerów, interfejsów, sterowników, a często także zmian w oprogramowaniu systemowym i aplikacjach. Wbudowane (embedded) MRAM w mikrokontrolerach mają już swoje nisze, natomiast duże systemy serwerowe wciąż przechodzą etap eksperymentów i wczesnych wdrożeń pilotażowych.

Do tego dochodzą kwestie kompatybilności z istniejącymi standardami modułów i interfejsów. MRAM może być prezentowana jako pamięć adresowana bajtowo (podobnie do DRAM) albo jako urządzenie blokowe (bliższe SSD). Każdy z tych wariantów wymaga innych kompromisów w projektowaniu i innych założeń po stronie systemu operacyjnego.

Przykładowe scenariusze użycia MRAM w serwerach

Najbardziej naturalne zastosowania MRAM w infrastrukturze serwerowej koncentrują się wokół obszarów, gdzie ulotność DRAM jest problemem, a opóźnienia NAND – zbyt wysokie.

Typowy scenariusz to nieulotne logi zapisu. Baza danych zapisuje dziennik transakcyjny (write-ahead log), który musi być trwały przed potwierdzeniem operacji klientowi. Dziś wymaga to zapisu na SSD lub macierz, co dodaje setki mikrosekund. Umieszczenie logu na warstwie MRAM pozwala skrócić ścieżkę zapisu do dziesiątek nanosekund lub pojedynczych mikrosekund, przy zachowaniu trwałości danych nawet po zaniku zasilania.

Inny przykład to nieulotny write-back cache w kontrolerach storage lub w warstwie programowej (np. w systemie plików czy warstwie obiektowej). Tradycyjnie stosuje się tu baterie lub superkondensatory podtrzymujące DRAM. MRAM umożliwia eliminację tych elementów, uproszczenie konstrukcji sprzętu i zmniejszenie ryzyka związanego z awarią zasilania w niekorzystnym momencie.

W scenariuszach HPC i AI rozważa się także użycie MRAM jako dodatkowej warstwy pamięci „blisko” akceleratorów GPU/TPU. Bufory modeli, wag czy danych treningowych mogłyby być utrzymywane w nieulotnej warstwie, co skraca czas restartu zadań po awarii i zmniejsza potrzebę przeładowywania dużych zbiorów z klasycznego storage.

Wreszcie, w serwerach o ograniczonej przestrzeni czy mocy (edge, urządzenia brzegowe) MRAM może zastąpić kombinację DRAM + NAND w pewnych rolach, zapewniając prostszą, jednorodną warstwę pamięci nieulotnej o szybszym dostępie. Tego typu zastosowania będą zapewne pojawiać się etapami, w niszach, gdzie przewaga funkcjonalna przeważy nad wyższym kosztem.

CXL – nowe „kręgosłupy” pamięci w serwerach

Dlaczego klasyczna magistrala pamięci przestaje wystarczać

W tradycyjnej architekturze serwera CPU łączy się z pamięcią DRAM przez kilka fizycznych kanałów. Każdy kanał obsługuje określoną liczbę modułów DIMM, a cała topologia jest stosunkowo sztywna. Zwiększenie pojemności pamięci oznacza dodawanie kolejnych modułów, co szybko napotyka ograniczenia elektryczne, mechaniczne i kosztowe.

Wraz ze wzrostem liczby rdzeni na gnieździe CPU rośnie zapotrzebowanie na pamięć na rdzeń. Jeżeli nie da się proporcjonalnie zwiększyć pojemności i przepustowości DRAM, dochodzi do zjawiska „przepełnionych” rdzeni – procesor ma moc obliczeniową, ale czeka na dane z pamięci. Dalsze dokładanie kanałów DRAM jest trudne technologicznie i obniża efektywność energetyczną.

Rozproszone systemy pamięciowe, typu NUMA, próbują ten problem łagodzić, ale dostęp do pamięci z innego węzła wiąże się ze wzrostem opóźnień. Do tego dochodzi rosnące zróżnicowanie typów pamięci: klasyczny DRAM, pamięć persystentna, przyspieszacze z własną pamięcią HBM, potencjalne moduły MRAM czy inne NVM.

CXL (Compute Express Link) powstał właśnie jako odpowiedź na tę rosnącą heterogeniczność i sztywność dotychczasowych interfejsów pamięciowych. Zakłada on, że pamięć przestaje być „przypisana na stałe” wyłącznie do kontrolera DRAM w CPU i staje się zasobem, który można przyłączać, współdzielić i zarządzać nim bardziej elastycznie.

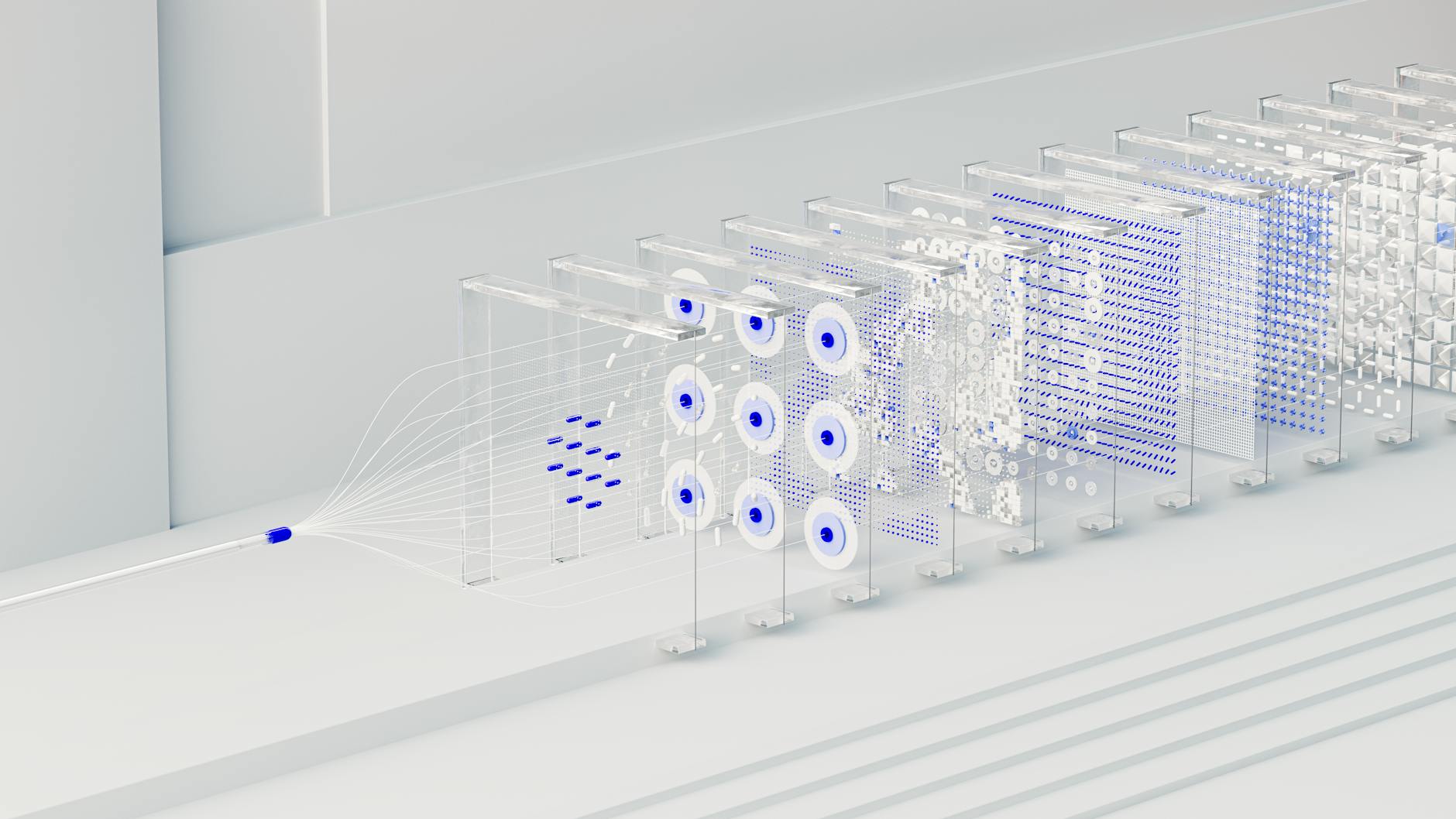

Podstawy architektury CXL

CXL jest protokołem działającym na fizycznej warstwie PCI Express, ale dodaje nad nią warstwę koherentnej komunikacji pamięciowej. Umożliwia to rozszerzenie przestrzeni adresowej hosta o pamięć znajdującą się na zewnętrznych urządzeniach, przy zachowaniu spójności cache pomiędzy CPU a tymi urządzeniami.

Specyfikacja CXL definiuje kilka podprotokołów, z których najbardziej istotne w kontekście pamięci to:

- CXL.io – odpowiednik klasycznego PCIe, służący do konfiguracji i komunikacji niepamięciowej,

- CXL.cache – umożliwia urządzeniu dostęp do pamięci hosta w sposób koherentny,

- CXL.mem – pozwala hostowi traktować pamięć urządzenia jako rozszerzenie własnej przestrzeni adresowej.

W przypadku urządzeń pamięciowych kluczowy jest właśnie CXL.mem. Moduł pamięci CXL może udostępniać swoją zawartość jako pamięć typu load/store, z adresowaniem bajtowym, którą CPU widzi podobnie do lokalnej pamięci głównej, choć z innymi parametrami opóźnienia i przepustowości.

Dzięki temu można projektować „pule pamięci” (memory pools) dostępne dla wielu serwerów lub gniazd CPU. Część pamięci pozostaje lokalna (przy kontrolerze DRAM), a część jest współdzielona i przyłączana przez CXL. Pojawia się tym samym kolejny poziom hierarchii, tym razem definiowany bardziej przez topologię interkonektu niż przez sam typ nośnika.

Typy urządzeń CXL a pamięć persystentna

Specyfikacja CXL rozróżnia kilka typów urządzeń, z których istotne dla tematu pamięci są w szczególności:

- Type 2 – akceleratory z własną pamięcią (np. GPU), które mogą mieć koherentny dostęp zarówno do pamięci hosta, jak i swojej,

- Type 3 – urządzenia pamięciowe udostępniające hostowi dodatkową pamięć przez CXL.mem.

Type 3 to naturalny kandydat na moduły z MRAM, innymi formami NVM lub nawet klasycznym DRAM, ale zarządzanym poza tradycyjnymi kanałami pamięci. Taki moduł może pełnić rolę:

- dodatkowej „warstwy” pamięci w serwerze o dużej pojemności,

- współdzielonego zasobu w klastrze (memory pooling),

- specjalizowanej, nieulotnej pamięci dostępnej jako load/store.

Pamięć persystentna podłączona przez CXL może być widziana przez system operacyjny jako NUMA node o innych parametrach – wolniejszy niż lokalny DRAM, ale znacznie szybszy niż tradycyjny storage. Daje to administratorowi i deweloperom aplikacji możliwość świadomego rozmieszczania danych: krytyczne struktury w DRAM, trwałe, ale mniej wrażliwe na opóźnienia – w persystentnej warstwie CXL.

Jak CXL zmienia myślenie o hierarchii pamięci

Przy klasycznym podejściu można było narysować dość prostą piramidę: cache L1–L3, DRAM, storage (SSD/HDD). Z CXL pojawiają się nowe węzły, które są gdzieś pomiędzy DRAM a SSD, a do tego mogą być współdzielone pomiędzy wieloma hostami.

W praktyce oznacza to, że hierarchia pamięci staje się bardziej „płaska” i elastyczna. Zamiast jednego, sztywnego poziomu pamięci głównej, można mieć:

- lokalny, szybki DRAM przy CPU,

- dodatkowy DRAM lub NVM na modułach CXL w tym samym serwerze,

- współdzielone zasoby pamięci CXL w ramach szafy lub kilku węzłów.

Każdy z tych poziomów ma inne opóźnienia i przepustowości, ale wszystkie są adresowane w modelu load/store, a nie jak urządzenia blokowe. Dla programisty oznacza to możliwość budowania struktur danych, które „przechodzą” przez granice fizycznych serwerów, a mimo to wyglądają jak zwykła pamięć, oczywiście przy zachowaniu ostrożności co do parametrów czasowych.

Systemy operacyjne i hipernadzorcy będą musiały rozwinąć bardziej zaawansowane polityki przydziału i migracji pamięci, podobne do dzisiejszych mechanizmów NUMA, ale z dodatkowymi kryteriami: ulotność/nieulotność, koszt jednostkowy, zapotrzebowanie na przepustowość, wymagania aplikacji co do opóźnień.

Połączenie MRAM z CXL – praktyczne modele użycia

Integracja MRAM z interfejsem CXL otwiera kilka modeli, które w dłuższej perspektywie mogą istotnie zmienić architekturę serwerów.

Pierwszy, najbardziej bezpośredni model to moduł pamięci typu 3, w którym MRAM jest prezentowana jako dodatkowy NUMA node o właściwościach: nieulotna, wolniejsza niż DRAM, ale nadal adresowana bajtowo. Taki moduł może pełnić rolę „pamięci rozszerzonej” dla dużych baz danych in-memory, które nie mieszczą się w DRAM, ale dla których przejście na SSD oznaczałoby zbyt duży spadek wydajności.

Drugi model to wspólny bank nieulotnej pamięci MRAM, dostępny przez CXL dla wielu hostów w szafie. Można tam umieszczać:

- współdzielone słowniki, modele ML, często używane zestawy danych referencyjnych,

- bufory wymiany pomiędzy zadaniami działającymi na różnych serwerach,

- trwałe kolejki zdarzeń lub logi, które nie znikają przy restarcie pojedynczych węzłów.

Tu persystencja MRAM łączy się z elastycznością CXL: dane pozostają dostępne nawet po wymianie hosta lub jego awarii, a jednocześnie są osiągalne z opóźnieniami znacznie niższymi niż przy dostępie do zewnętrznego storage przez sieć.

Trzeci model dotyczy akceleratorów. Moduł z GPU lub dedykowanym ASIC może mieć na pokładzie własną MRAM, udostępnianą hostowi przez CXL.cache/CXL.mem jako przestrzeń wymiany danych. Usuwa to część kopiowań pomiędzy pamięcią karty a pamięcią hosta i umożliwia przechowywanie niektórych struktur bezpośrednio w nieulotnej pamięci akceleratora.

W każdym z tych modeli istotne jest, aby oprogramowanie rozumiało różnice pomiędzy poziomami hierarchii. Nawet jeśli z perspektywy instrukcji CPU wszystko jest „pamięcią”, to parametry opóźnienia i trwałości wymagają świadomego doboru: co umieścić w DRAM, co w MRAM przez CXL, a co nadal trzymać na klasycznym storage.

Konsekwencje dla systemów operacyjnych i oprogramowania

Pojawienie się nieulotnej pamięci load/store w połączeniu z CXL wymusza zmiany nie tylko w sprzęcie, ale przede wszystkim w warstwie systemowej.

System operacyjny musi obsłużyć nowe klasy węzłów NUMA, rozróżnić pamięć ulotną i nieulotną, zarządzać mapowaniem przestrzeni adresowej oraz zapewnić mechanizmy bezpiecznego użycia persystentnej pamięci (np. flush cache, bariery zapisu). Modele programistyczne oparte jedynie na systemach plików i blokowym I/O stają się zbyt ograniczone, gdy aplikacja może zapisywać struktury danych bezpośrednio w trwałej pamięci bajtowo adresowanej.

Już dziś trwają prace nad bibliotekami i frameworkami do obsługi persystentnej pamięci (jak PMDK w świecie Intel/Optane). Podobne podejścia będą adaptowane do nowych nośników, w tym MRAM, i nowych interfejsów, w tym CXL. Chodzi o to, aby programista nie musiał samodzielnie rozwiązywać kwestii takich jak:

- jak zapewnić atomowość i spójność struktur danych w nieulotnej pamięci,

- jak odtwarzać stan po niekontrolowanym restarcie,

- jak minimalizować liczbę kosztownych operacji flush przy zachowaniu wymaganego poziomu trwałości.

W praktyce można się spodziewać, że pierwsze będą korzystać z takich możliwości bazy danych, silniki kolejkowe, systemy przetwarzania strumieniowego i komponenty odpowiedzialne za krytyczne logi. To tam zysk z niskolatencyjnej, trwałej pamięci jest najbardziej bezpośredni, a inwestycja w dostosowanie kodu – najłatwiejsza do uzasadnienia biznesowo.

Dla typowych aplikacji biznesowych ważniejsze stanie się z kolei to, aby systemy pośrednie (bazy, cache, warstwy messagingowe) potrafiły używać MRAM i CXL w sposób przeźroczysty. Z perspektywy dewelopera aplikacji kluczowe będzie rozumienie, że „pamięć” nie jest już jednorodnym zasobem, a wybory konfiguracyjne (np. gdzie trzymać sesje, kolejki, cache) mają coraz większe przełożenie na koszt i przewidywalność pracy systemu.

Modele programistyczne dla persystentnej pamięci load/store

Persystentna pamięć adresowana bajtowo wymusza porzucenie prostego założenia, że „restart = czyste środowisko”. Dane mogą trwać dłużej niż procesy, a nawet dłużej niż sam system operacyjny. To otwiera możliwości, ale też generuje nowe obowiązki po stronie programistów i architektów.

Najczęściej rozważa się trzy główne podejścia do korzystania z takiej pamięci:

- tryb plikowy na DAX – persystentna pamięć jest widoczna jako specjalny filesystem (np. ext4-DAX, XFS-DAX), a aplikacja mapuje pliki w przestrzeń adresową procesów (mmap). Dostęp nadal odbywa się „przez pliki”, ale bez buforowania w page cache,

- tryb „pamięć jako pamięć” – system widzi NVM/MRAM jako dodatkowy NUMA node, a aplikacja korzysta z niego przez zwykłe alokacje pamięci (malloc/new) wspierane przez odpowiednie biblioteki i polityki alokatora,

- tryb hybrydowy – metadane i wskaźniki przetrzymywane są w formie „plikowej”, a duże bufory danych lub cache działają jako pamięć NUMA z własnym zarządzaniem.

W pierwszym modelu łatwiej wykorzystać istniejące narzędzia (backup, snapshoty, zarządzanie uprawnieniami), kosztem dodatkowej warstwy abstrakcji. Drugi model jest najbliższy temu, jak programiści myślą o pamięci w kodzie C/C++ czy Rust – struktury danych „po prostu tam są” po restarcie, o ile aplikacja zadba o poprawne opróżnianie cache i spójność.

W praktyce sporo systemów o wysokich wymaganiach dostępności wybiera model hybrydowy: najważniejsze wskaźniki i metadane są zapisywane w strukturach zaprojektowanych z myślą o persystencji (z logiem zmian, walidacją, wersjonowaniem), a duże bloki danych mogą być nadpisywane bardziej swobodnie, przy mniejszej liczbie gwarancji.

Trwałość, atomowość i spójność – nowe „ACID” w pamięci

Gdy baza danych pracuje na SSD, transakcje i log WAL są dobrze znanym mechanizmem zapewniania trwałości. Gdy dane znajdują się bezpośrednio w MRAM pod CXL, klasyczne założenia trzeba doprecyzować: część operacji odbywa się w cache CPU, a dopiero później trafia do persystentnego nośnika.

Aby zapisać dane „naprawdę”, nie wystarczy wykonać zwykłego zapisu do wskaźnika. Konieczne są dodatkowe kroki:

- wymuszenie opróżnienia linii cache (np. instrukcjami typu

clwb/clflushopt), - zastosowanie bariery pamięci (memory fence), aby zachować kolejność operacji,

- w niektórych przypadkach dodatkowe potwierdzenie po stronie urządzenia (np. gdy MRAM jest za kontrolerem z własnym buforem).

Stąd też w bibliotekach typu PMDK logika transakcyjna jest odwzorowana w kodzie: każda modyfikacja struktur w nieulotnej pamięci jest otoczona sekwencją zapis–flush–fence–walidacja. Na poziomie abstrakcji programisty można to ukryć za konstrukcjami w stylu „transakcji w pamięci” lub „persystentnych wskaźników”, ale pod spodem dzieje się dużo więcej niż przy zwykłym malloc.

CXL komplikuje obraz o tyle, że ścieżka do pamięci może być dłuższa, a dane mogą być buforowane po drodze (np. w kontrolerach, switchach). Specyfikacja i implementacje sprzętowe muszą zatem zapewnić spójny model trwałości: jeśli CPU otrzyma potwierdzenie wykonania flush, dane powinny przetrwać awarię zasilania urządzenia CXL. Deweloperom systemowym dochodzi więc dodatkowy wymiar testów: nie tylko crash procesu, ale i symulacje utraty jednego z węzłów pamięciowych.

Bezpieczeństwo danych w rozproszonych przestrzeniach pamięci

Kiedy pamięć staje się współdzielonym zasobem w skali szafy lub klastra, pytanie „kto co może zobaczyć” nabiera nowego znaczenia. Ochrona danych nie kończy się na interfejsie sieciowym – dostęp load/store przez CXL bywa dla aplikacji szybszy i bardziej „bezpośredni” niż tradycyjne I/O.

W praktyce oznacza to kilka wymagań, które zwykle trzeba uwzględnić już na etapie projektu:

- izolacja przestrzeni adresowych – IOMMU, rozszerzenia SMMU oraz mechanizmy w samym CXL muszą precyzyjnie określać, które urządzenie i który host może adresować daną pulę pamięci,

- szyfrowanie w spoczynku – MRAM jako pamięć nieulotna powinna zwykle być szyfrowana sprzętowo, bo fizyczne wyniesienie modułu z szafy nie jest scenariuszem czysto teoretycznym,

- kontrola tożsamości hostów – węzeł, który zgłasza się po zasób CXL, musi zostać uwierzytelniony, a najlepiej także autoryzowany z uwzględnieniem roli/tenantów,

- przydział i zwalnianie zasobów – po odłączeniu hosta lub zmianie przypisania puli pamięci nie może dojść do „przecieku” pozostałości danych do innego klienta.

Vendorzy platform serwerowych zaczęli już łączyć koncepcje typu TEE (Trusted Execution Environment) czy SEV/TDX z warstwą pamięciową. Rozszerzenie tego na zewnętrzne moduły CXL jest kolejnym krokiem: nie wystarczy szyfrować DRAM, jeżeli w MRAM pozostają obrazy danych użytkownika sprzed kilku tygodni.

Ekonomika: gdzie MRAM i CXL mają największy sens

Nawet jeśli technologia jest atrakcyjna, wdrożenie zawsze sprowadza się do pytania o koszt jednostkowy i łączny koszt posiadania (TCO). MRAM pozostaje droższa niż DRAM w przeliczeniu na gigabajt i prawdopodobnie tak będzie jeszcze przez dłuższy czas. Z drugiej strony może zastępować zarówno DRAM (jako warstwa „wolniejszej” pamięci głównej), jak i część storage (jako najszybsza, trwała warstwa danych).

Najczęściej wskazuje się kilka scenariuszy, w których połączenie MRAM+CXL bywa opłacalne mimo wyższego kosztu modułów:

- systemy o krytycznym czasie wznowienia – bazy danych, systemy transakcyjne, platformy brokerskie, gdzie utrata cache lub danych in-memory po awarii skutkuje długą rekoncyliacją i oknem niedostępności,

- środowiska z dużym, współdzielonym zbiorem danych „gorących” – modele ML, tabele referencyjne, słowniki, które muszą być współdzielone przez wiele węzłów bez replikacji w każdym z nich,

- systemy o bardzo nieregularnych wzorcach dostępu – gdzie tradycyjne podejścia z SSD/NVMe i agresywnym cachingiem nie zapewniają wystarczająco przewidywalnego czasu odpowiedzi.

Rozszerzalność CXL ma też konsekwencje budżetowe. Zamiast kupować serwery „maksymalnie wypchane DRAM-em”, można budować konfiguracje z mniejszą lokalną pamięcią, ale podłączane do jednej, większej puli. Daje to elastyczność: po zmianie obciążenia nie trzeba wymieniać wszystkich hostów, wystarczy inaczej przydzielić pamięć z puli CXL lub dołożyć pojedyncze moduły w szafie.

Projektowanie aplikacji „świadomych hierarchii pamięci”

Kolejnym krokiem jest wprowadzenie „świadomości lokalizacji” do samych aplikacji. Do tej pory programiści często przyjmowali, że każda przydzielona pamięć ma podobne parametry (o ile nie przekroczymy limitu RAM i nie wejdziemy w swap). W świecie DRAM+MRAM+CXL takie podejście bywa kosztowne.

Jednym z praktycznych wzorców jest jawny podział struktur danych na klasy:

- „gorące” i niewielkie – tablice indeksów, liczniki, stany sesji; zwykle trzymane w lokalnym DRAM,

- „duże, ale tolerujące opóźnienia” – słowniki, modele, rzadko aktualizowane konfiguracje; dobre kandydatury do MRAM w tym samym serwerze,

- „współdzielone, trwałe” – logi, kolejki międzyserwerowe, snapshoty stanów; typowo trzymane w MRAM dostępnej przez CXL jako zasób współdzielony.

Taki podział może być wspierany przez same frameworki. Wyobrażalny jest np. ORM lub biblioteka cache, która przy inicjalizacji klas encji określa „tier” pamięci. Przy późniejszym wdrożeniu CXL wystarcza precyzyjniejsza konfiguracja mapowania: encje typu A zawsze w DRAM, typu B preferencyjnie w MRAM lokalnej, typu C – w MRAM współdzielonej.

Nawet prosta aplikacja webowa, korzystająca z Redis/Memcached i bazy SQL, może odczuć zmianę: cache klastrów sesji użytkowników trzymany w MRAM przez CXL przetrwa restart całego front-endu. Odpada problem „zimnego cache”, a ruch w stronę bazy w pierwszych minutach po uruchomieniu zostaje znacząco ograniczony.

Wpływ na architekturę klastrów i systemów rozproszonych

Możliwość współdzielenia pamięci w skali szafy naturalnie skłania do ponownego przemyślenia niektórych założeń systemów rozproszonych. Dotyczy to w szczególności:

- replikacji – jeśli węzły mają dostęp do wspólnej, trwałej pamięci, część replikacji może zostać zastąpiona mechanizmami logowania do współdzielonego obszaru i odtwarzania stanu,

- koordynacji – prymitywy synchronizacji (locki rozproszone, semafory, bariery) mogą bazować na strukturach pamięci współdzielonej zamiast na protokołach sieciowych z dodatkowymi hopami,

- shardingu – dane mogą być rozkładane po węzłach nie tylko według logiki aplikacyjnej, ale również z uwzględnieniem topologii pamięci: co jest blisko którego hosta, a które fragmenty muszą być naprawdę współdzielone.

Nie oznacza to jednak „powrotu do pamięci współdzielonej” znanej z systemów SMP na sterydach. Opóźnienia i zmienność ścieżki CXL nadal mają znaczenie. Bardziej realistyczny obraz to hybryda: aplikacja nadal myśli w kategoriach węzłów i repliki, ale niektóre koszty – jak logowanie, odtwarzanie stanu czy wymiana „gorących” metadanych – ulegają redukcji dzięki temu, że pewne struktury znajdują się w MRAM dostępnej ze wszystkich hostów.

MRAM jako „czarny skrzynka” serwera

Jednym z ciekawszych, często niedocenianych zastosowań MRAM w serwerach jest rola trwałego magazynu diagnostycznego. Niewielka ilość tej pamięci, ściśle kontrolowana przez firmware i BMC, może gromadzić:

- logi sprzętowe i zdarzenia z warstwy firmware (POST, MCE, korekcja ECC),

- minimalne zrzuty pamięci w razie panic/kernel crash,

- metryki dotyczące zachowania modułów CXL, akceleratorów i samych CPU.

Z uwagi na nieulotność MRAM dane tego typu mogą utrzymać się przez wielokrotne restarty, a nawet przez wymianę niektórych komponentów. Dla operatora centrum danych oznacza to możliwość dokładniejszej analizy przyczyn rzadkich, trudnych do odtworzenia awarii. W odróżnieniu od zapisu na dysk, który może być niedostępny w krytycznym momencie, zapis do MRAM działa w ścisłej współpracy z firmware i kontrolerami pamięci.

CXL poszerza ten model o scenariusz, w którym część tych danych jest trzymana w module dostępny dla wielu hostów, ale zapisywany jest wyłącznie przez zaufane komponenty (np. kontrolery BMC). Serwer, który uległ awarii, może pozostawić tam swój „odcisk palca”, a analiza odbywa się z innego węzła, już po jego fizycznej wymianie.

Integracja z istniejącymi technologiami pamięci masowej

Wprowadzenie MRAM i CXL nie eliminuje potrzeby klasycznego storage, ale zmienia sposób, w jaki organizuje się całe drzewo pamięci masowej. Pojawiają się np. konfiguracje, w których:

- MRAM pełni funkcję write-back cache dla SSD/NVMe – dane trafiają najpierw do nieulotnej pamięci load/store, gdzie są agregowane i porządkowane, a dopiero później spływają sekwencyjnie na nośnik blokowy,

- warstwa plikowa korzysta z MRAM jako metadata store, a właściwe dane plików przechowuje na SSD; przyspiesza to operacje intensywnie korzystające z metadanych (np. katalogi, małe pliki),

- w systemach obiektowych (S3-compatible) MRAM jest miejscem przechowywania indeksów i mapowania obiektów, co zmniejsza czas lookupu kosztem dodatkowej warstwy sprzętowej.

Te konfiguracje bywają transparentne z punktu widzenia aplikacji: widzi ona nadal „zwykły” filesystem lub endpoint S3, ale opóźnienia i przepustowość wyglądają inaczej. W praktyce wymaga to jednak zmian po stronie sterowników i systemów plików, które muszą rozumieć charakterystykę MRAM (w tym jej trwałość, ale też potencjalne ograniczenia wytrzymałości przy bardzo intensywnym zapisie).

Ścieżka migracji: od prototypów do produkcji

Przejście na nowe technologie pamięciowe rzadko odbywa się skokowo. Zwykle najpierw pojawiają się niewielkie pilotaże, testy A/B i scenariusze „best effort”, w których awaria nowej warstwy nie wpływa na integralność danych, a jedynie na wydajność.

Praktyczny, stopniowy scenariusz wdrożenia MRAM+CXL może obejmować:

- Etap „cache przy bazie danych” – MRAM jest używana jako dodatkowy, trwały cache logów lub indeksów. Wszystkie dane nadal są utrzymywane na dysku, a MRAM jedynie skraca ścieżkę przy typowych obciążeniach.

- Amdahl’s Law in the Multicore Era. IEEE Computer Society (2008) – Analiza ograniczeń skalowania CPU i wąskich gardeł pamięci

- The Memory System: You Can’t Avoid It, You Can’t Ignore It, You Can’t Fake It. Synthesis Lectures on Computer Architecture / Morgan & Claypool (2013) – Przegląd hierarchii pamięci, opóźnień cache, DRAM i storage

- Computer Architecture: A Quantitative Approach, 6th Edition. Morgan Kaufmann (2019) – Modelowanie wydajności, m.in. mur pamięci, cache miss, NUMA

- JEDEC Standard JESD79-5: DDR5 SDRAM. JEDEC Solid State Technology Association (2020) – Parametry techniczne DRAM, przepustowość, zasilanie i skalowanie

- Nonvolatile Memory Technologies with Emphasis on Flash: A Comprehensive Guide to Understanding and Using Flash Memory Devices. IEEE Press / Wiley (2010) – Charakterystyka NAND, opóźnienia, trwałość i rola w hierarchii pamięci

- Magnetoresistive Random Access Memory (MRAM): Present and Future. Nature Electronics (2019) – Przegląd technologii MRAM, szybkość, nieulotność i zastosowania serwerowe

- Compute Express Link (CXL) Specification 3.0. Compute Express Link Consortium (2022) – Standard CXL, tryby pamięci, rozszerzanie pojemności i pooling

- The Landscape of Persistent Memory. Communications of the ACM (2020) – Omówienie pamięci nieulotnych w pobliżu CPU i ich wpływu na systemy

Najczęściej zadawane pytania (FAQ)

Dlaczego pamięć jest dziś głównym wąskim gardłem w serwerach?

Współczesne procesory mają bardzo wiele rdzeni i rozbudowane cache L1/L2/L3, dlatego same obliczenia rzadko są problemem. Wąskie gardło powstaje w momencie, gdy rdzenie muszą czekać na dane z pamięci DRAM, która nie nadąża z przepustowością i czasem dostępu.

Różnica pomiędzy szybkością cache a RAM ciągle rośnie, a przepaść między RAM i SSD jest jeszcze większa. W zastosowaniach intensywnie korzystających z pamięci – jak bazy in-memory, analityka, AI – to właśnie opóźnienia i przepustowość RAM decydują o tym, ile realnie „wyciśnie” się z CPU.

Na czym polega „mur pamięci” (memory wall) w serwerach?

„Mur pamięci” to sytuacja, w której procesor jest znacznie szybszy niż system pamięci i przez sporą część czasu czeka na dane. Teoretycznie serwer ma dużą moc obliczeniową, ale praktycznie nie jest w stanie jej wykorzystać, bo kolejne odwołania do RAM powodują przerwania cache miss i rosnące opóźnienia.

Widać to dobrze w hurtowniach danych trzymanych w pamięci: serwer z dziesiątkami rdzeni powinien obsłużyć wiele zapytań, a w praktyce wąskim gardłem staje się dostęp do RAM. Dodawanie kolejnych rdzeni niewiele zmienia, bo ograniczeniem nie jest już logika CPU, tylko przepustowość pamięci.

Jakie ograniczenia ma DRAM jako pamięć główna serwera?

DRAM jest szybki i relatywnie tani, ale ma kilka istotnych ograniczeń. Po pierwsze jest ulotny – po zaniku zasilania traci dane, więc nie może pełnić roli trwałego repozytorium. Po drugie, każdy kontroler pamięci w CPU obsługuje tylko określoną liczbę kanałów i modułów, co ogranicza maksymalną pojemność.

Dodatkowo rosnąca gęstość chipów zwiększa zużycie energii i problemy z chłodzeniem. Przy bardzo dużej liczbie modułów pojawiają się też wyzwania sygnałowe i większe opóźnienia. Utrzymanie rozsądnego „RAM na rdzeń” staje się coraz droższe i wymaga skomplikowanych konfiguracji – zwłaszcza w systemach NUMA.

Czym MRAM różni się od DRAM i NAND (SSD)?

MRAM to pamięć nieulotna, która co do zasady łączy cechy DRAM i NAND. Jest znacznie szybsza niż klasyczna pamięć flash NAND i pod względem opóźnień zbliża się do DRAM, a jednocześnie zachowuje dane po wyłączeniu zasilania. Dzięki temu może funkcjonować jako dodatkowy poziom pamięci między RAM a SSD.

W praktyce MRAM może zmniejszyć liczbę operacji zapisu na NAND (odciążając SSD) i skrócić ścieżkę do danych, które muszą być zarówno szybkie, jak i trwałe – np. logi transakcyjne, metadane baz danych czy bufory systemów czasu rzeczywistego.

Co to jest CXL i jak pomaga w walce z wąskim gardłem pamięci?

CXL (Compute Express Link) to interfejs pozwalający elastyczniej podłączać pamięć i akceleratory do CPU niż tradycyjne kanały DRAM. Dzięki CXL można do serwera dołączyć dodatkowe zasoby pamięci jako osobne urządzenia, a nie tylko jako moduły DIMM w gniazdach przy procesorze.

W efekcie rośnie dostępna pojemność pamięci i możliwości jej współdzielenia między serwerami, bez konieczności rozbudowy liczby gniazd CPU. CXL otwiera drogę do budowy tzw. pamięci składowej (pooled memory), która ogranicza marnowanie zasobów i pomaga obejść fizyczne limity klasycznej szyny pamięci.

Jakie są praktyczne skutki wąskich gardeł pamięci dla firm?

Najczęstszy skutek to „skalowanie przez dokładanie serwerów” zamiast rozbudowy pamięci w istniejących maszynach. Zamiast jednego dużego serwera z odpowiednią ilością RAM, organizacja kupuje kilka mniejszych – rosną koszty licencji, sieci, obudów i utrzymania.

Dodatkowo, gdy licencjonowanie jest powiązane z liczbą rdzeni CPU, firma płaci za moc obliczeniową, której realnie nie może wykorzystać, bo system blokuje się na pamięci. W usługach czasu rzeczywistego i AI przekłada się to na niestabilne opóźnienia i konieczność stosowania złożonych mechanizmów cache’owania po stronie aplikacji.

Czy MRAM i CXL zastąpią DRAM w serwerach?

W dającej się przewidzieć perspektywie DRAM zwykle pozostanie podstawową pamięcią główną. MRAM i CXL raczej rozszerzają hierarchię pamięci niż całkowicie zastępują istniejące warstwy. Pozwalają dodać nowe poziomy – szybkiej, nieulotnej pamięci – oraz elastyczniej zarządzać jej pojemnością.

W praktyce oznacza to, że serwery będą coraz częściej korzystać z mieszanki: cache i DRAM blisko CPU, za nimi warstwa pamięci nieulotnej (np. MRAM lub inne NVM) dostępnej przez CXL, a dopiero dalej klasyczne SSD/HDD. Dzięki temu „mur pamięci” może zostać znacząco odsunięty, a koszt na gigabajt i wat bardziej przewidywalny.